This article is part of my series of projects around Ternary Computing and Processor Design. Click here to see the list of projects of this series.

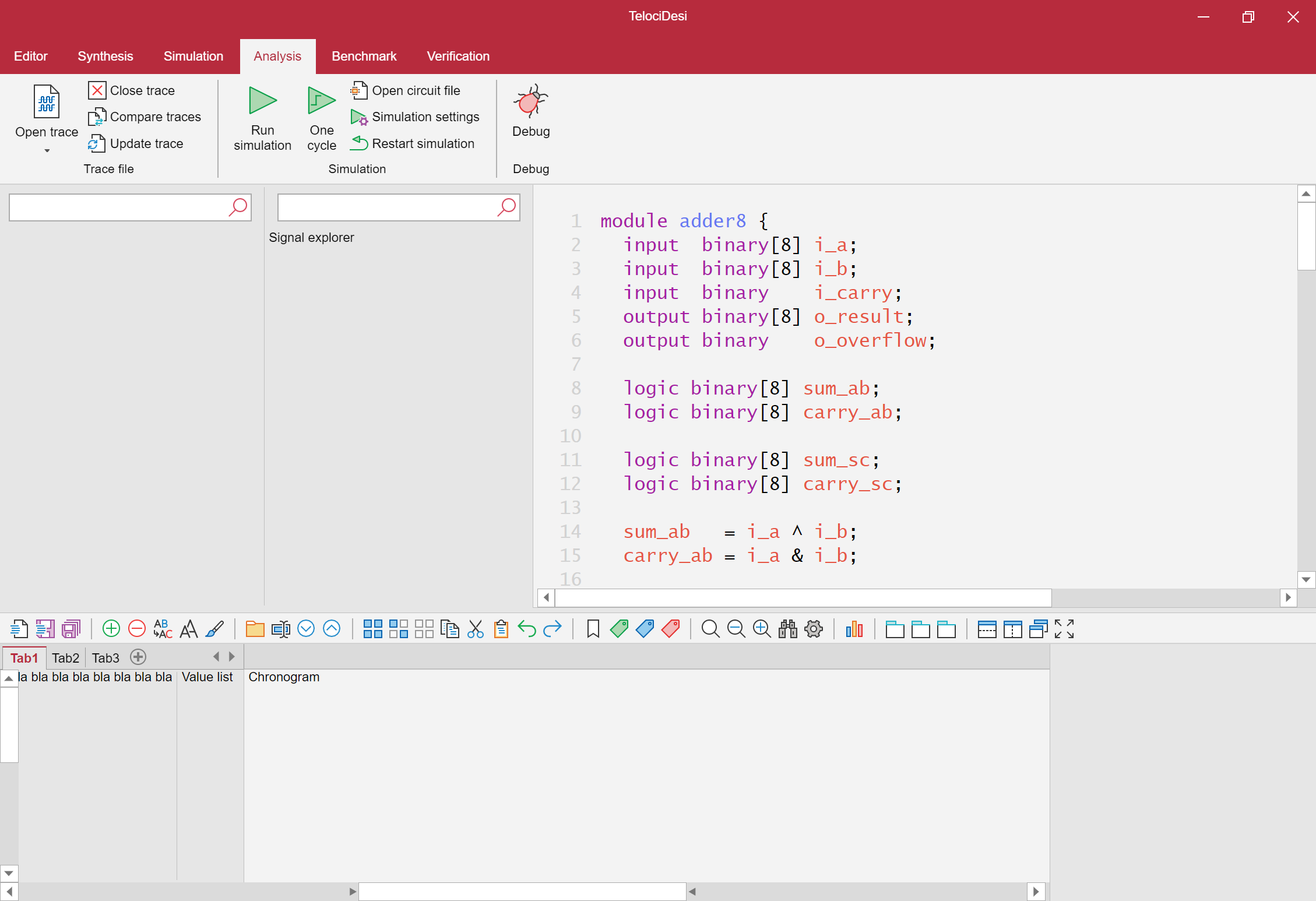

This project is the first part in the creation of a development environment for TernaryVerilog. The goal is to include and unify the tools I am developing for coding and synthesizing TernaryVerilog, exploring and debugging the circuits, launching simulations and benchmarks, visualize signal traces, verify the functions of modules, study the impact of design parameters, calculate the maximum frequency of a circuit and identify the critical path, and much more.

In order to make the UI flexible, portable and easier to develop, I decided to use Electron for this project. Electron allows the use of web technologies (HTML, CSS and JS) for standalone programs. It actually consists of a lighter version of the Chromium web renderer and a node server. The front-end uses script languages and markup languages and will communicate via ZeroMQ (a cross-platform cross-language wrapper for sockets) to the Python TernaryVerilog synthesizer and the C++ circuit simulator.

Screenshot of the WIP software

The development of this program will take a very long time of course, but this first step consisted mostly in building the UI and planning for the implementation of the key features. As I develop new tools, I will try to connect them to TelociDesi.

The name TelociDesi stands for Ternary Logic Circuit Designer and Simulator. It was used for a project I did a while ago which was basically a clone of Simulink customized for ternary logic circuits.

This article is part of my series of projects around Ternary Computing and Processor Design. Click here to see the list of projects of this series.

Go back to the list of projects